# MAGNACHIP SEMICONDUCTOR LTD. 8-BIT SINGLE-CHIP MICROCONTROLLERS WITH EMBEDDED FLASH

HMS99C51S HMS99C52S HMS99C54S HMS99C56S HMS99C58S

User's Manual (Ver. 1.01)

### **Revision History**

Ver 1.01 (Sep, 10, 2004) this book

The company name, Hynix Semiconductor Inc. changed to MagnaChip Semiconductor Ltd.

Ver 1.0 (Dec, 01, 2003) The first released document.

Version 1.01

Published by MCU Application Team

©2004 MagnaChip Semiconductor Ltd. All right reserved.

Additional information of this manual may be served by MagnaChip semiconductor offices in Korea or Distributors and Representatives listed at address directory.

MagnaChip semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, MagnaChip semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

# **CONTENTS**

| DEVICE NAMING STRUCTURE                   | 1  |

|-------------------------------------------|----|

| HMS99C51S/52S/54S/56S/58S SELECTION GUIDE | 1  |

| FEATURE                                   | 2  |

| PIN CONFIGURATION                         | 4  |

| PIN DEFINITIONS AND FUNCTIONS             | 8  |

| FUNCTIONAL DESCRIPTION                    | 11 |

| CPU                                       | 12 |

| SPECIAL FUNCTION REGISTERS                | 13 |

| X2 MODE                                   | 19 |

| TIMER / COUNTER 0 AND 1                   | 21 |

| TIMER 2                                   | 22 |

| SERIAL INTERFACE (UART)                   | 23 |

| INTERRUPT SYSTEM                          | 24 |

| POWER SAVING MODES                        | 26 |

| ELECTRICAL CHARACTERISTICS                | 27 |

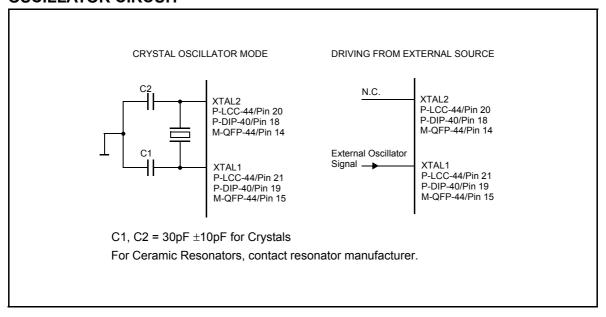

| OSCILLATOR CIRCUIT                        | 39 |

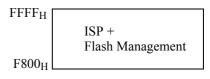

| FLASH MEMORY                              | 43 |

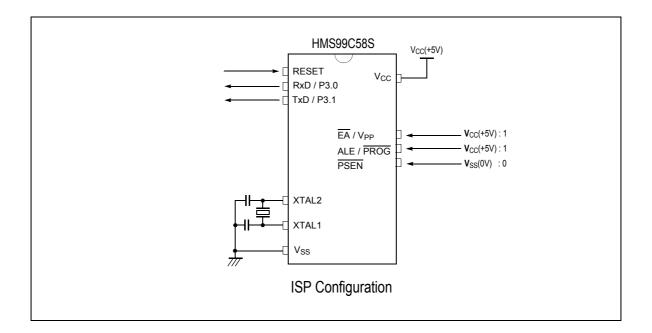

| IN-SYSTEM PROGRAMMING (ISP)               | 55 |

| ISP METHOD FOR PC (MAGNACHIP WINISP)      | 66 |

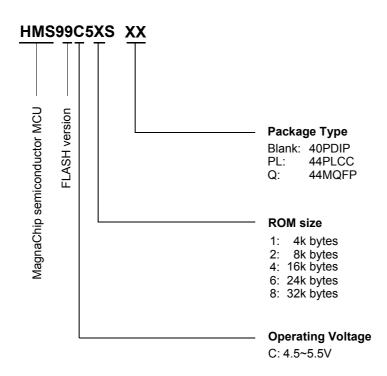

## **DEVICE NAMING STRUCTURE**

## HMS99C51S/52S/54S/56S/58S SELECTION GUIDE

| Operating   | ROM size (bytes)              | RAM size | Davies Name                                                   | Operating       |

|-------------|-------------------------------|----------|---------------------------------------------------------------|-----------------|

| Voltage (V) | FLASH                         | (bytes)  | Device Name                                                   | Frequency (MHz) |

| 4.5~5.5     | 4K<br>8K<br>16K<br>24K<br>32K | 256      | HMS99C51S<br>HMS99C52S<br>HMS99C54S<br>HMS99C56S<br>HMS99C58S | 40              |

### **FEATURE**

- Fully compatible to standard MCS-51 microcontroller

- Wide operating frequency up to 40MHz (for more detail, See "HMS99C51S/52S/54S/56S/58S SELECTION GUIDE" on page 1)

- X2 Speed Improvement capability (X2 Mode: 6 clocks/machine cycle)

20MHz @5V (Equivalent to 40MHz @5V)

- ISP(In-System Programming) using Standard V<sub>CC</sub> Power Supply

- · Boot ROM Contains Low Level FLASH Programming Routines and a Default Serial Loader

- 4K/8K/16K/24K/32K bytes FLASH user program memory

- Byte Write and Block(2K, 8K Bytes) Erase

- · 2K bytes FLASH boot loader

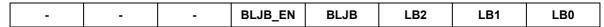

- 1 byte Hardware Security Byte (HSB)

- 256 bytes RAM

- · 64K bytes external program memory space

- · 64K bytes external data memory space

- · Four 8-bit ports

- Three 16-bit Timers / Counters (Timer2 with up/down counter feature)

- UART

- · One clock output port

- Programmable ALE pin enable / disable (Low EMI)

- Six interrupt sources, two priority levels

- Power saving Idle and power down mode

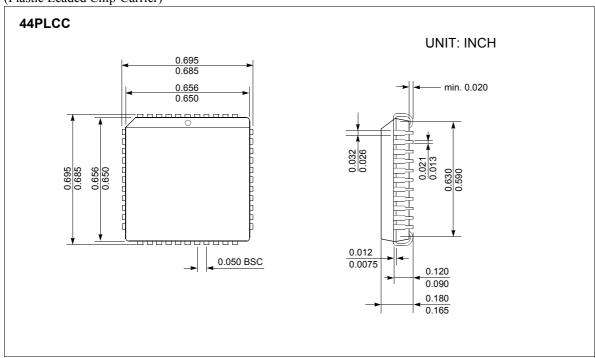

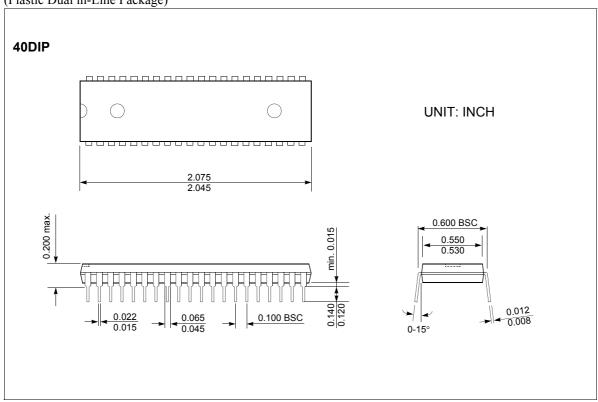

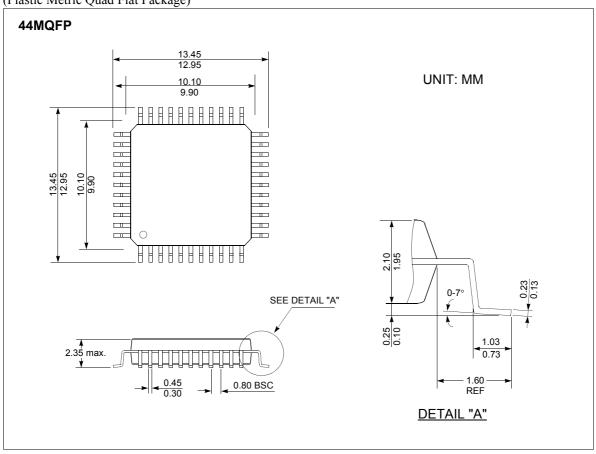

- P-DIP-40, P-LCC-44, P-MQFP-44 package

- Temperature Ranges : -40°C ~ 85°C

### Description

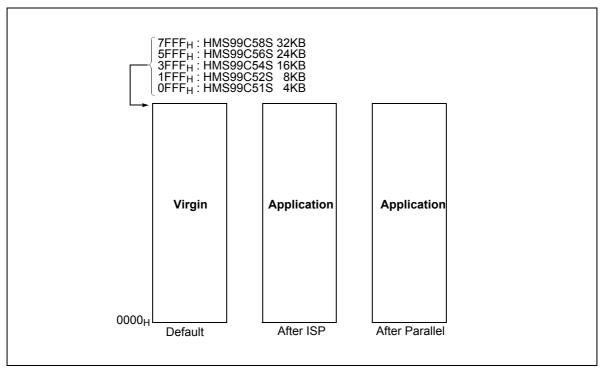

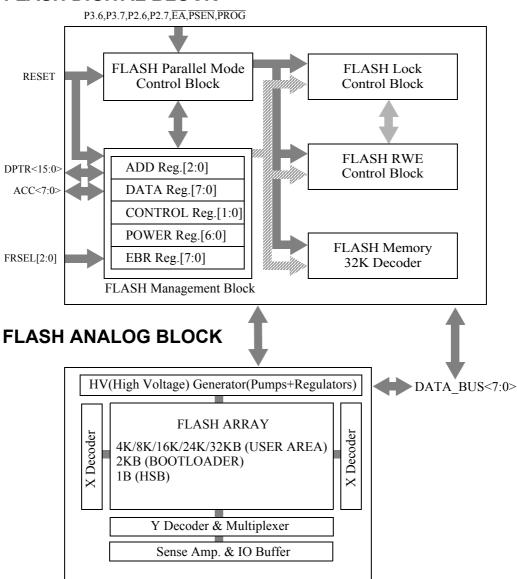

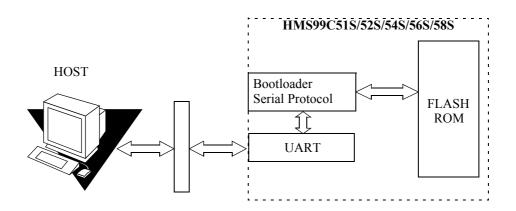

The Flash memory increases EPROM and ROM functionality with in-circuit electrical erasure and programming. It contains 4K, 8K, 16K, 24K or 32K bytes of program memory. This memory is both parallel and serial In-System Programmable(ISP). The ISP allows devices to alter their own program memory in the actual end product under software control through UART ports. A default serial loader(bootloader) program supports ISP of the Flash memory. The programming does not require external 12V programming voltage. The necessary high programming voltage is generated on-chip using the standard  $V_{\rm CC}$  pins of the microcontroller.

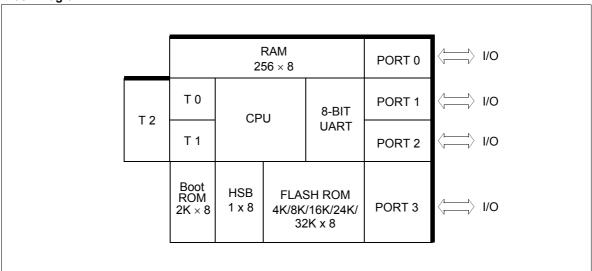

**Block Diagram**

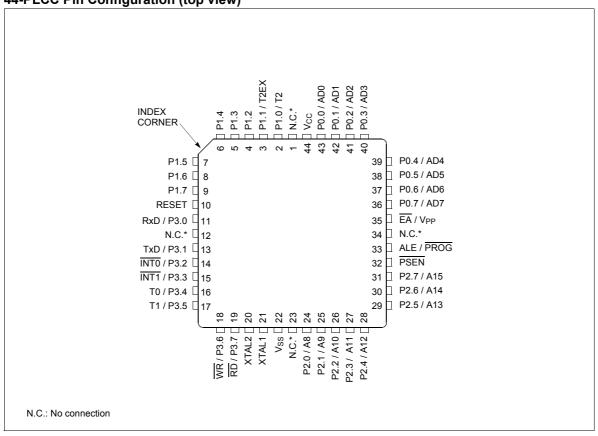

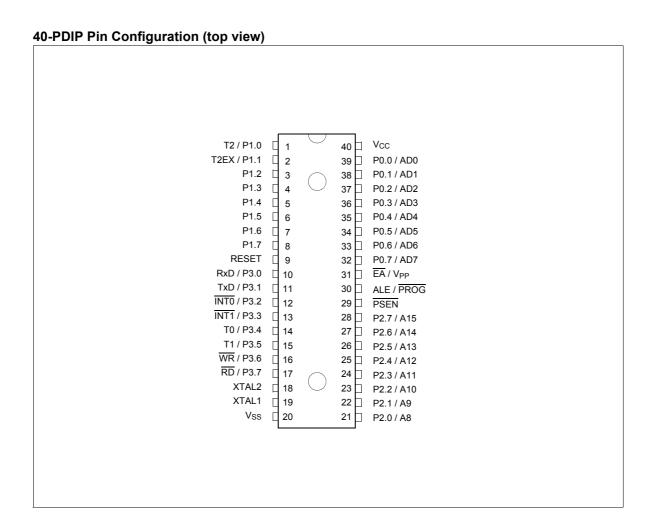

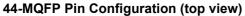

## PIN CONFIGURATION

## 44-PLCC Pin Configuration (top view)

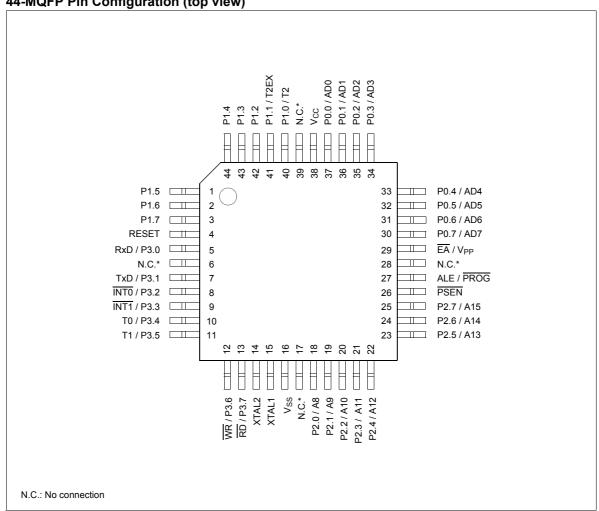

**Logic Symbol**

# PIN DEFINITIONS AND FUNCTIONS

|           | Pin Number   |             | er            | Input/ |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------|--------------|-------------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol    | PLCC-<br>44  | PDIP-<br>40 | MQFP-<br>44   | Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| P1.0-P1.7 | 2-9          | 1-8         | 40-44,<br>1-3 | I/O    | Port1 Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-up resistors and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the pulls-ups (I <sub>IL</sub> , in the DC characteristics). Port1 also serves alternate functions of Timer 2 as follows.                   |  |  |

|           | 2            | 1           | 40            |        | P1.0 / T2, Clock Out : Timer/counter 2 external count input, Clock Out P1.1 / T2EX :Timer/counter 2 trigger input                                                                                                                                                                                                                                                                                                              |  |  |

|           | 3            | 2           | 41            |        | Port1 receives the low-order address bytes during Flash programming and verifying.                                                                                                                                                                                                                                                                                                                                             |  |  |

| P3.0-P3.7 | 11,<br>13-19 | 10-17       | 5, 7-13       | I/O    | Port 3  Port 3 is an 8-bit bidirectional I/O port with interna pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors and can be used as inputs. As inputs, port 3 pins that are externally pulled low will source current because of the pulls-ups (I <sub>IL</sub> , in the DC characteristics). Port 3 also serves the special features of the 80C51 family, as listed below. |  |  |

|           | 11           | 10          | 5             |        | P3.0 / RxD receiver data input (asynchronous) or data input/output(synchronous) of serial interface 0                                                                                                                                                                                                                                                                                                                          |  |  |

|           | 13           | 11          | 7             |        | P3.1 / TxD transmitter data output (asynchronous) or clock output (synchronous) of the serial interface 0                                                                                                                                                                                                                                                                                                                      |  |  |

|           | 14           | 12          | 8             |        | P3.2 /INTO interrupt 0 input/timer 0 gate control                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           | 15           | 13          | 9             |        | P3.3 / INT1 interrupt 1 input/timer 1 gate control                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|           | 16           | 14          | 10            |        | P3.4 /T0 counter 0 input                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|           | 17           | 15          | 11            |        | P3.5 /T1 counter 1 input                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|           | 18<br>19     | 16<br>17    | 12            |        | P3.6 / WR the write control signal latches the data byte from port 0 into the external data memory P3.7 /RD the read control signal enables the external data memory to port 0                                                                                                                                                                                                                                                 |  |  |

| XTAL2     | 20           | 18          | 14            | 0      | XTAL2 Output of the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|           | F           | Pin Numbe   | er          | Innut/           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------|-------------|-------------|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol    | PLCC-<br>44 | PDIP-<br>40 | MQFP-<br>44 | Input/<br>Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| XTAL1     | 21          | 19          | 15          | ı                | Input to the inverting oscillator amplifier and input to the internal clock generator circuits. To drive the device from an external clock source, XTAL1 should be driven, while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is divided down by a divide-by-two flip-flop. Minimum and maximum high and low times as well as rise and fall times specified in the AC characteristics must be observed.                                                                                                                                                                                                                                                                                   |  |  |  |

| P2.0-P2.7 | 24-31       | 21-28       | 18-25       | I/O              | Port 2 Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-up resistors and can be used as inputs. As inputs, port 2 pins that are externally pulled low will source current because of the pulls-ups (I <sub>IL</sub> , in the DC characteristics). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application it uses strong internal pull-ups when outputting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 special function register.  Some Port 2 pins receive the high-order address bits |  |  |  |

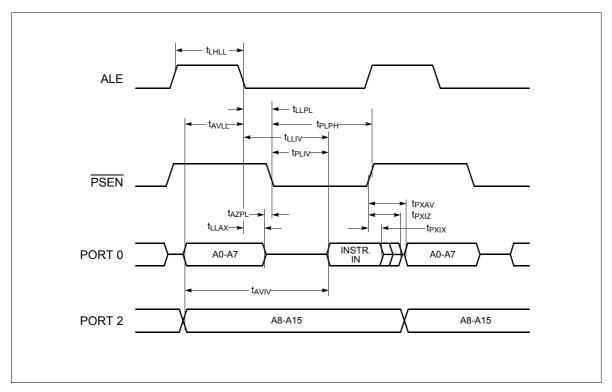

| PSEN      | 32          | 29          | 26          | 0                | during flash program, verify, and erase operations.  The Program Store Enable  The read strobe to external program memory wher the device is executing code from the external program memory. PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RESET     | 10          | 9           | 4           | I                | RESET A high level on this pin for two machine cycles while the oscillator is running resets the device. The port pins will be driven to their reset condition when a minimum V <sub>IH</sub> voltage is applied whether the oscillator is running or not. An internal diffused resistor to V <sub>SS</sub> permits power-on reset using only an external capacitor to V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                      | F             | Pin Numbe   | er            | Immust/          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|----------------------|---------------|-------------|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol               | PLCC-<br>44   | PDIP-<br>40 | MQFP-<br>44   | Input/<br>Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ALE /<br>PROG        | 33            | 30          | 27            | 0                | The Address Latch Enable / Program pulse  Output pulse for latching the low byte of the address during an access to external memory. In norma operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pir is also the program pulse input (PROG) during EPROM programming.  If desired, ALE operation can be disabled by setting bit 0 of SFR location 8E <sub>H</sub> . With this bit set, the pin is weakly pulled high. The ALE disable feature will be terminated by reset. Setting the ALE-disable bit has no affect if the microcontroller is in external executior mode. |  |  |  |

| EA / V <sub>PP</sub> | 35            | 31          | 29            | I                | External Access Enable / Program Supply Voltage<br>EA must be externally held low to enable the device to fetch code from external program memory locations<br>0000 <sub>H</sub> to FFFF <sub>H</sub> . If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than its internal memory size. This pin also receives the 12.75V programming supply voltage (V <sub>PP</sub> ) during EPROM programming.  Note; however, that if any of the Lock bits are                                                                                                                                                                                                              |  |  |  |

|                      |               |             |               |                  | programmed, EA will be internally latched on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| P0.0-P0.7            | 36-43         | 32-39       | 30-37         | I/O              | Port 0 Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application it uses strong internal pull-ups when emitting 1s. Port 0 also receives and outputs the code bytes during program and verification respectively in the GMS99X5X. External pull-up resistors are required during program verification.                                                                                                                                                                                                         |  |  |  |

| V <sub>SS</sub>      | 22            | 20          | 16            | -                | Circuit ground potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| V <sub>C</sub> C     | 44            | 40          | 38            | -                | Supply terminal for all operating modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| N.C.                 | 1,12<br>23,34 | -           | 6,17<br>28,39 | -                | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

## **FUNCTIONAL DESCRIPTION**

The HMS99C51S/52S/54S/56S/58S are fully compatible to the standard 8051 microcontroller family.

It is compatible with the general 8051 family, while maintaining all architectural and operational characteristics of the general 8051 family.

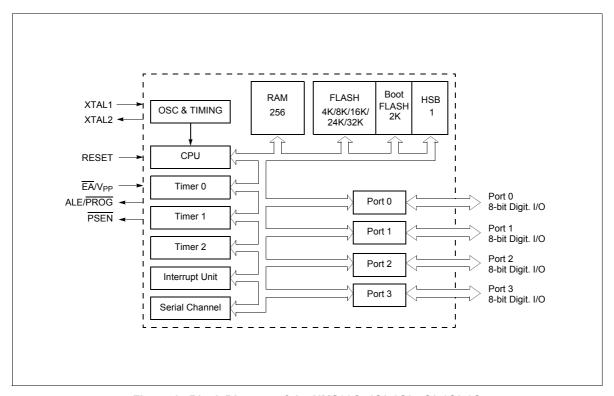

Figure 1 shows a block diagram of the HMS99C51S/52S/54S/56S/58S.

Figure 1. Block Diagram of the HMS99C51S/52S/54S/56S/58S

## **CPU**

The HMS99C51S/52S/54S/56S/58S are efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44% one-byte, 41% two-byte, and 15% three-byte instructions. With a 12 MHz crystal, 58% of the instructions are executed in  $1.0\mu s$  (40MHz: 300ns).

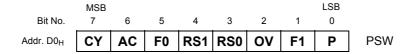

### **Special Function Register PSW**

| В                       | it                             | Function                                                                                                                                                                                                                                                                                           |

|-------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С                       | Υ                              | Carry Flag                                                                                                                                                                                                                                                                                         |

| Α                       | С                              | Auxiliary Carry Flag (for BCD operations)                                                                                                                                                                                                                                                          |

| F                       | 0                              | General Purpose Flag                                                                                                                                                                                                                                                                               |

| RS1<br>0<br>0<br>1<br>1 | <b>RS0</b><br>0<br>1<br>0<br>1 | Register Bank select control bits  Bank 0 selected, data address 00 <sub>H</sub> - 07 <sub>H</sub> Bank 1 selected, data address 08 <sub>H</sub> - 0F <sub>H</sub> Bank 2 selected, data address 10 <sub>H</sub> - 17 <sub>H</sub> Bank 3 selected, data address 18 <sub>H</sub> - 1F <sub>H</sub> |

| 0                       | V                              | Overflow Flag                                                                                                                                                                                                                                                                                      |

| F                       | 1                              | General Purpose Flag                                                                                                                                                                                                                                                                               |

| F                       |                                | Parity Flag Set/cleared by hardware each instruction cycle to indicate an odd/even number of "one" bits in the accumulator, i.e. even parity.                                                                                                                                                      |

Reset value of PSW is 00<sub>H</sub>.

## **SPECIAL FUNCTION REGISTERS**

All registers, except the program counter and the four general purpose register banks, reside in the special function register area.

The 28 special function registers (SFR) include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. There are also 128 directly addressable bits within the SFR area.

All SFRs are listed in Table 1, Table 2, and Table 3.

In Table 1 they are organized in numeric order of their addresses. In Table 2 they are organized in groups which refer to the functional blocks of the HMS99C51S/52S/54S/56S/58S. Table 3 illustrates the contents of the SFRs

| Address         | Register                | Contents after<br>Reset             | Address         | Register         | Contents after<br>Reset             |

|-----------------|-------------------------|-------------------------------------|-----------------|------------------|-------------------------------------|

| 80 <sub>H</sub> | P0 <sup>1)</sup>        | FF <sub>H</sub>                     | 88 <sub>H</sub> | TCON 1)          | 00н                                 |

| 81 <sub>H</sub> | SP                      | 07 <sub>H</sub>                     | 89 <sub>H</sub> | TMOD             | 00 <sub>H</sub>                     |

| 82 <sub>H</sub> | DPL                     | 00 <sub>H</sub>                     | 8A <sub>H</sub> | TL0              | 00 <sub>H</sub>                     |

| 83 <sub>H</sub> | DPH                     | 00 <sub>H</sub>                     | 8B <sub>H</sub> | TL1              | 00 <sub>H</sub>                     |

| 84 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 8C <sub>H</sub> | TH0              | 00 <sub>H</sub>                     |

| 85 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 8D <sub>H</sub> | TH1              | 00 <sub>H</sub>                     |

| 86 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 8E <sub>H</sub> | AUXR0            | XXH 2)                              |

| 87 <sub>H</sub> | PCON                    | 0XXX0000 <sub>B</sub> <sup>2)</sup> | 8F <sub>H</sub> | CKCON            | XXXXXXX0 <sub>B</sub> <sup>2)</sup> |

| 90 <sub>H</sub> | <b>P1</b> 1)            | FF <sub>H</sub>                     | 98 <sub>H</sub> | SCON 1)          | 00 <sub>H</sub>                     |

| 91 <sub>H</sub> | reserved                | 00 <sub>H</sub>                     | 99 <sub>H</sub> | SBUF             | XX <sub>H</sub> <sup>2)</sup>       |

| 92 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 9A <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| 93 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 9B <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| 94 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 9C <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| 95 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 9D <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| 96 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 9E <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| 97 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | 9F <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| A0 <sub>H</sub> | <b>P2</b> <sup>1)</sup> | FF <sub>H</sub>                     | A8 <sub>H</sub> | IE <sup>1)</sup> | 0X00000 <sub>B</sub> <sup>2)</sup>  |

| A1 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | A9 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| A2 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | AA <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| A3 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | AB <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| A4 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | AC <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| A5 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | AD <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| A6 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | AE <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| A7 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | AF <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| B0 <sub>H</sub> | P3 <sup>1)</sup>        | FF <sub>H</sub>                     | B8 <sub>H</sub> | IP <sup>1)</sup> | XX000000 <sub>B</sub> <sup>2)</sup> |

| B1 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | B9 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| B2 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | BA <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| B3 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | BB <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| B4 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | BC <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| B5 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | BD <sub>H</sub> | reserved         | XX <sup>2)</sup>                    |

| B6 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | BE <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

| B7 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>       | BF <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>       |

Table 1. Special Function Registers in Numeric Order of their Addresses (cont'd)

| Address         | Register      | Contents after<br>Reset             | Address         | Register          | Contents after<br>Reset              |

|-----------------|---------------|-------------------------------------|-----------------|-------------------|--------------------------------------|

| C0 <sub>H</sub> | reserved      | XX <sub>H</sub>                     | C8 <sub>H</sub> | T2CON 1)          | 00н                                  |

| C1 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | C9 <sub>H</sub> | T2MOD             | XXXXXXX00 <sub>B</sub> <sup>2)</sup> |

| C2 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | CAH             | RC2L 1)           | 00 <sub>H</sub>                      |

| C3 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | CB <sub>H</sub> | RC2H 1)           | 00 <sub>H</sub>                      |

| C4 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | CCH             | TL2 <sup>1)</sup> | 00 <sub>H</sub>                      |

| C5 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | CD <sub>H</sub> | TH2 <sup>1)</sup> | 00 <sub>H</sub>                      |

| C6 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | CE <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| C7 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | CF <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D0 <sub>H</sub> | <b>PSW</b> 1) | FF <sub>H</sub>                     | D8 <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D1 <sub>H</sub> | FCON 3)       | XXXX0000 <sub>B</sub> <sup>2)</sup> | D9 <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D2 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | DA <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D3 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | DB <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D4 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | DC <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D5 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | $DD_H$          | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D6 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | DE <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| D7 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | DF <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E0 <sub>H</sub> | ACC 1)        | 00 <sub>H</sub>                     | E8 <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E1 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | E9 <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E2 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | EA <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E3 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | EB <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E4 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | ECH             | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E5 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | ED <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E6 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | EEH             | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| E7 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | EFH             | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F0 <sub>H</sub> | <b>B</b> 1)   | 00 <sub>H</sub>                     | F8 <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F1 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | F9 <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F2 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | FA <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F3 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | FB <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F4 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | FC <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F5 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | FD <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F6 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | FE <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

| F7 <sub>H</sub> | reserved      | XX <sub>H</sub> <sup>2)</sup>       | FF <sub>H</sub> | reserved          | XX <sub>H</sub> <sup>2)</sup>        |

Table 1. Special Function Registers in Numeric Order of their Addresses (cont'd)

<sup>1)</sup> Bit-addressable Special Function Register.

<sup>2)</sup> X means that the value is indeterminate and the location is reserved.

<sup>3)</sup> FCON access is reserved for the ISP software.

| Block                                       | Symbol                                   | Name                                                                                                                                                                             | Address                                                                                                                          | Contents<br>after Reset                                                                                        |  |

|---------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| CPU                                         | ACC<br>B<br>DPH<br>DPL<br>PSW<br>SP      | Accumulator B-Register Data Pointer, High Byte Data Pointer, Low Byte Program Status Word Register Stack Pointer                                                                 | E0 <sub>H</sub> <sup>1)</sup> F0 <sub>H</sub> <sup>1)</sup> 83 <sub>H</sub> 82 <sub>H</sub> D0 <sub>H</sub> <sup>1)</sup>        | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>07 <sub>H</sub> |  |

| Interrupt System                            | IE<br>IP                                 | Interrupt Enable Register<br>Interrupt Priority Register                                                                                                                         | A8 <sub>H</sub> <sup>1)</sup><br>B8 <sub>H</sub> <sup>1)</sup>                                                                   | 0X000000 <sub>B</sub> <sup>2)</sup><br>XX000000 <sub>B</sub> <sup>2)</sup>                                     |  |

| Ports                                       | P0<br>P1<br>P2<br>P3                     | Port 0<br>Port 1<br>Port 2<br>Port 3                                                                                                                                             | 80 <sub>H</sub> <sup>1)</sup><br>90 <sub>H</sub> <sup>1)</sup><br>A0 <sub>H</sub> <sup>1)</sup><br>B0 <sub>H</sub> <sup>1)</sup> | FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub>                                                          |  |

| Serial Channels                             | PCON 3)<br>SBUF<br>SCON                  | Power Control Register<br>Serial Channel Buffer Reg.<br>Serial Channel 0 Control Reg.                                                                                            | 87 <sub>H</sub><br>99 <sub>H</sub><br><b>98<sub>H</sub></b> <sup>1)</sup>                                                        | 0XXX0000 <sub>B</sub> <sup>2)</sup><br>XX <sub>H</sub> <sup>2)</sup><br>00 <sub>H</sub>                        |  |

| Timer 0/ Timer 1                            | TCON<br>TH0<br>TH1<br>TL0<br>TL1<br>TMOD | Timer 0/1 Control Register Timer 0, High Byte Timer 1, High Byte Timer 0, Low Byte Timer 1, Low Byte Timer Mode Register                                                         | 88 <sub>H</sub> <sup>1)</sup><br>8C <sub>H</sub><br>8D <sub>H</sub><br>8A <sub>H</sub><br>8B <sub>H</sub><br>89 <sub>H</sub>     | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                    |  |

| Timer 2 T2CON T2MOD RC2H RC2L TH2 TL2 AUXR0 |                                          | Timer 2 Control Register Timer 2 Mode Register Timer 2 Reload Capture Reg., High Byte Timer 2 Reload Capture Reg., Low Byte Timer 2, High Byte Timer 2, Low Byte Aux. Register 0 | C8 <sub>H</sub> <sup>1)</sup> C9 <sub>H</sub> CB <sub>H</sub> CA <sub>H</sub> CC <sub>H</sub> 8E <sub>H</sub>                    | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>XXXXXXXX0B <sup>2</sup>                                              |  |

| Power Saving<br>Modes                       | PCON 3)                                  | Power Control Register                                                                                                                                                           | 87 <sub>H</sub>                                                                                                                  | 0XXX0000 <sub>B</sub> <sup>2)</sup>                                                                            |  |

| FLASH                                       | FCON 4)                                  | Flash Control Register                                                                                                                                                           | D1 <sub>H</sub>                                                                                                                  | XXXX0000 <sub>B</sub> <sup>2)</sup>                                                                            |  |

Table 2. Special Function Registers - Functional Blocks

- 1) Bit-addressable Special Function register

- 2) X means that the value is indeterminate and the location is reserved

- 3) This special function register is listed repeatedly since some bit of it also belong to other functional blocks

- 4) This special function register is reserved for the ISP software.

| Address         | Register | Bit 7 | 6   | 5   | 4   | 3    | 2   | 1   | 0    |

|-----------------|----------|-------|-----|-----|-----|------|-----|-----|------|

| 80 <sub>H</sub> | P0       |       |     |     |     |      |     |     |      |

| 81 <sub>H</sub> | SP       |       |     |     |     |      |     |     |      |

| 82 <sub>H</sub> | DPL      |       |     |     |     |      |     |     |      |

| 83 <sub>H</sub> | DPH      |       |     |     |     |      |     |     |      |

| 87 <sub>H</sub> | PCON     | SMOD  | -   | -   | -   | GF1  | GF0 | PDE | IDLE |

| 88 <sub>H</sub> | TCON     | TF1   | TR1 | TF0 | TR0 | IE1  | IT1 | IE0 | IT0  |

| 89 <sub>H</sub> | TMOD     | GATE  | C/T | M1  | MT  | GATE | C/T | M1  | MO   |

| 8A <sub>H</sub> | TL0      |       |     |     |     |      |     |     |      |

| 8B <sub>H</sub> | TL1      |       |     |     |     |      |     |     |      |

| 8C <sub>H</sub> | TH0      |       |     |     |     |      |     |     |      |

| 8D <sub>H</sub> | TH1      |       |     |     |     |      |     |     |      |

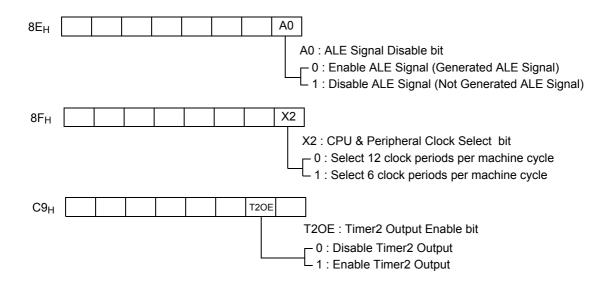

| 8E <sub>H</sub> | AUXR0    | -     | -   | -   | -   | -    | -   | -   | A0   |

| 8F <sub>H</sub> | CKCON    | -     | -   | -   | -   | -    | -   | -   | X2   |

| 90 <sub>H</sub> | P1       |       |     |     |     |      |     |     |      |

| 98 <sub>H</sub> | SCON     | SM0   | SM1 | SM2 | REN | TB8  | RB8 | TI  | RI   |

| 99 <sub>H</sub> | SBUF     |       |     |     |     |      |     |     |      |

| A0 <sub>H</sub> | P2       |       |     |     |     |      |     |     |      |

| A8 <sub>H</sub> | IE       | EA    | -   | ET2 | ES  | ET1  | EX1 | ET0 | EX0  |

| B0 <sub>H</sub> | P3       |       |     |     |     |      |     |     |      |

| B8 <sub>H</sub> | IP       | -     | -   | PT2 | PS  | PT1  | PX1 | PT0 | PX0  |

Table 3. Contents of SFRs, SFRs in Numeric Order

|  |  |  |  | SFR bit and byte addressable |

|--|--|--|--|------------------------------|

|  |  |  |  | SFR not bit addressable      |

<sup>- :</sup> this bit location is reserved

| Address         | Register | Bit 7  | 6      | 5      | 4        | 3      | 2         | 1       | 0       |

|-----------------|----------|--------|--------|--------|----------|--------|-----------|---------|---------|

| C8 <sub>H</sub> | T2CON    | TF2    | EXF2   | RCLK   | TCLK     | EXEN2  | TR2       | C/T2    | CP/RL2  |

| C9 <sub>H</sub> | T2MOD    | -      | -      | -      | -        | -      | -         | T20E †  | DCEN    |

| $CA_H$          | RC2L     |        |        |        |          |        |           |         |         |

| CB <sub>H</sub> | RC2H     |        |        |        |          |        |           |         |         |

| ССн             | TL2      |        |        |        |          |        |           |         |         |

| CD <sub>H</sub> | TH2      |        |        |        |          |        |           |         |         |

| D0 <sub>H</sub> | PSW      | CY     | AC     | F0     | RS1      | RS0    | OV        | F1      | Р       |

| D1 <sub>H</sub> | FCON     | FRSEL2 | FRSEL1 | FRSEL0 | ERASESEL | ENBOOT | INTROM_EN | PGMSEL1 | PGMSEL0 |

| E0 <sub>H</sub> | ACC      |        |        |        |          |        |           |         |         |

| F0 <sub>H</sub> | В        |        |        |        |          |        |           |         |         |

Table 3. Contents of SFRs, SFRs in Numeric Order (cont'd)

|  |  |  |  | SFR bit and byte addressable |

|--|--|--|--|------------------------------|

|  |  |  |  | SFR not bit addressable      |

-: this bit location is reserved

### X2 MODE

The HMS99C51S/52S/54S/56S/58S core needs only 6 clock periods per machine cycle in X2 mode. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- · Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

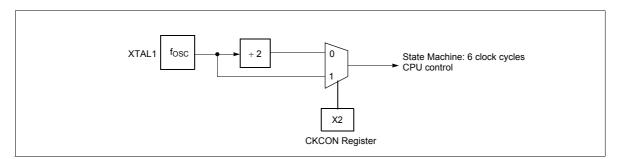

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

### **X2** Mode Description

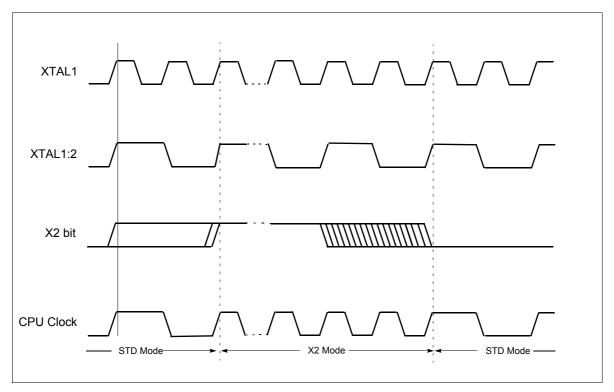

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 2. shows the clock generation block diagram. X2 bit is validated on XTAL1±2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 3. shows the mode switching waveforms:

Figure 2. Clock Generation Diagram

The X2 bit in the CKCON register allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature(X2 mode).

#### **CAUTION**

In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers) will have their time reference divided by two. For example a free running timer generating an interrupt every 30 ms will then generate an interrupt every 15 ms. UART with 2400 baud rate will have 4800 baud rate.

Figure 3. Mode Switching Waveforms

.

20 Sep. 2004 Ver 1.01

### **TIMER / COUNTER 0 AND 1**

Timer/Counter 0 and 1 can be used in four operating modes as listed in Table 4:

| Mode | Description                                                                       |      | TM  | IOD |    | Input Clock               |                           |  |

|------|-----------------------------------------------------------------------------------|------|-----|-----|----|---------------------------|---------------------------|--|

| Wode | Description                                                                       | Gate | C/T | M1  | MO | internal                  | external (Max.)           |  |

| 0    | 8-bit timer/counter with a divide-by-32 prescaler                                 | Х    | Х   | 0   | 0  | f <sub>OSC</sub> ÷(12×32) | f <sub>OSC</sub> ÷(24×32) |  |

| 1    | 16-bit timer/counter                                                              | Х    | Χ   | 0   | 1  | f <sub>OSC</sub> ÷12      | f <sub>OSC</sub> ÷24      |  |

| 2    | 8-bit timer/counter with 8-bit auto-reload                                        | Х    | Х   | 1   | 0  | f <sub>OSC</sub> ÷12      | f <sub>OSC</sub> ÷24      |  |

| 3    | Timer/counter 0 used as one 8-bit timer/counter and one 8-bit timer Timer 1 stops | Х    | Х   | 1   | 1  | f <sub>OSC</sub> ÷12      | f <sub>OSC</sub> ÷24      |  |

Table 4. Timer/Counter 0 and 1 Operating Modes

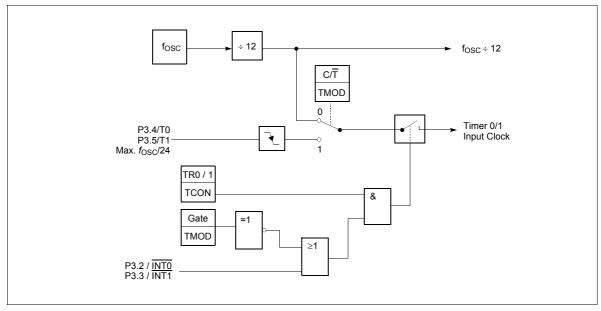

In the "timer" function ( $C/\overline{T}$  = "0") the register is incremented every machine cycle. Therefore the count rate is  $f_{OSC}/12$ .

In the "counter" function the register is incremented in response to a 1-to-0 transition at its corresponding external input pin (P3.4/T0, P3.5/T1). Since it takes two machine cycles to detect a falling edge the max. count rate is  $f_{OSC}/24$ . External inputs  $\overline{INT0}$  and  $\overline{INT1}$  (P3.2, P3.3) can be programmed to function as a gate to facilitate pulse width measurements. Figure 4 illustrates the input clock logic.

Figure 4. Timer/Counter 0 and 1 Input Clock Logic

## TIMER 2

Timer 2 is a 16-bit timer/Counter with an up/down count feature. It can operate either as timer or as an event counter which is selected by bit  $C/\overline{T2}$  (T2CON.1). It has three operating modes as shown in Table 5.

|                        | T2CON              |            |     | T2M<br>OD | T2C<br>ON | P1.      |                                             | Input Clock           |                               |

|------------------------|--------------------|------------|-----|-----------|-----------|----------|---------------------------------------------|-----------------------|-------------------------------|

| Mode                   | RCLK<br>or<br>TCLK | CP/<br>RL2 | TR2 | DCE<br>N  | EXE<br>N2 | T2<br>EX | Remarks                                     | internal              | external<br>(P1.0/T2)         |

| 16-bit Auto-<br>Reload | 0                  | 0          | 1   | 0         | 0         | Х        | reload upon over-<br>flow                   | f <sub>OSC</sub> ÷ 12 | Max.<br>f <sub>OSC</sub> ÷24  |

|                        | 0                  | 0          | 1   | 0         | 1         | <b>\</b> | reload trigger<br>(falling edge)            |                       |                               |

|                        | 0                  | 0          | 1   | 1         | Х         | 0        | Down counting                               |                       |                               |

|                        | 0                  | 0          | 1   | 1         | Х         | 1        | Up counting                                 |                       |                               |

| 16-bit<br>Capture      | 0                  | 1          | 1   | Х         | 0         | Х        | 16 bit Timer/<br>Counter (only up-          | f <sub>OSC</sub> ÷ 12 | Max.<br>f <sub>OSC</sub> ÷ 24 |

|                        | 0                  | 1          | 1   | х         | 1         | <b>\</b> | counting)<br>capture TH2,TL2<br>→ RC2H,RC2L |                       |                               |

| Baud Rate<br>Generator | 1                  | Х          | 1   | Х         | 0         | Х        | no overflow interrupt request               | f <sub>OSC</sub> ÷ 12 | Max.<br>f <sub>OSC</sub> ÷ 24 |

|                        | 1                  | X          | 1   | Х         | 1         | <b>\</b> | (TF2) extra external interrupt ("Timer 2")  |                       |                               |

| Off                    | Х                  | Х          | 0   | Х         | Х         | Х        | Timer 2 stops                               | -                     | -                             |

Table 5. Timer/Counter 2 Operating Modes

Note: ↓ = ¬Lfalling edge

# **SERIAL INTERFACE (UART)**

The serial port is full duplex and can operate in four modes (one synchronous mode, three asynchronous modes) as illustrated in Table 6. The possible baud rates can be calculated using the formulas given in Table 7.

| Mode  | SCON |     | Baudrate                                     | Description                                                                                                       |  |  |  |

|-------|------|-----|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Wiode | SM0  | SM1 | Baudrate                                     | ·                                                                                                                 |  |  |  |

| 0     | 0    | 0   | f <sub>OSC</sub><br>12                       | Serial data enters and exits through RxD. TxD outputs the shift clock. 8-bit are transmitted/received (LSB first) |  |  |  |

| 1     | 0    | 1   | Timer 1/2 overflow rate                      | 8-bit UART<br>10 bits are transmitted (through TxD) or<br>received (RxD)                                          |  |  |  |

| 2     | 1    | 0   | $\frac{f_{OSC}}{32}$ or $\frac{f_{OSC}}{64}$ | 9-bit UART<br>11 bits are transmitted (TxD) or received (RxD)                                                     |  |  |  |

| 3     | 1    | 1   | Timer 1/2 overflow rate                      | 9-bit UART<br>Like mode 2 except the variable baud rate                                                           |  |  |  |

**Table 6. UART Operating Modes**

| Baud Rate<br>derived from               | Interface Mode | Baudrate                                                             |  |  |

|-----------------------------------------|----------------|----------------------------------------------------------------------|--|--|

| Oscillator                              | 0              | f <sub>osc</sub><br>12                                               |  |  |

| Oscillator                              | timer) vith    | $\frac{2^{SMOD}}{64} \times f_{OSC}$                                 |  |  |

| Timer 1 (16-bit timer)                  | 1,3            | $\frac{2^{SMOD}}{32} \times (Timer \ 1 \ overflow)$                  |  |  |

| (8-bit timer with<br>8-bit auto reload) | 1,3            | $\frac{2^{SMOD}}{32} \times \frac{f_{OSC}}{12 \times [256 - (TH1)]}$ |  |  |

| Timer 2                                 | 1,3            | $\frac{f_{\text{OSC}}}{32 \times [65536 - (RC2H, RC2L)]}$            |  |  |

Table 7. Formulas for Calculating Baud rates

## **INTERRUPT SYSTEM**

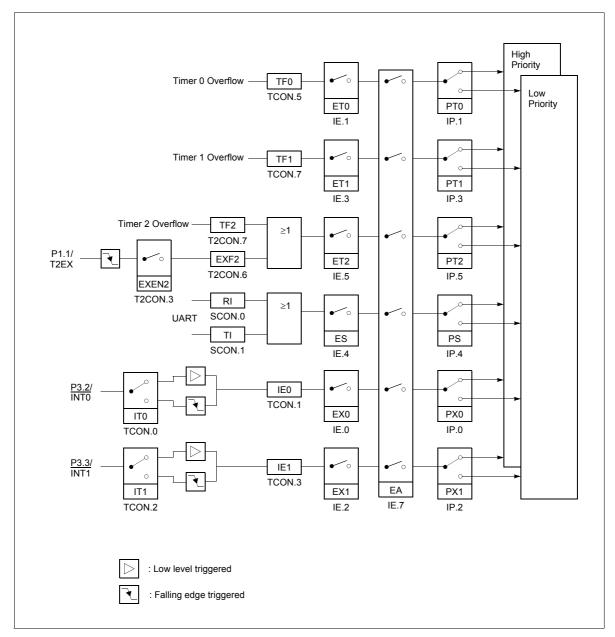

The HMS99C51S/52S/54S/56S/58S provide 6 (above 8K bytes ROM version) interrupt sources with two priority levels. Figure 5 gives a general overview of the interrupt sources and illustrates the request and control flags.

Figure 5. Interrupt Request Sources

| Source (Request Flags) | Vectors               | Vector Address    |

|------------------------|-----------------------|-------------------|

| RESET                  | RESET                 | 0000 <sub>H</sub> |

| IE0                    | External interrupt 0  | 0003 <sub>H</sub> |

| TF0                    | Timer 0 interrupt     | 000B <sub>H</sub> |

| IE1                    | External interrupt 1  | 0013 <sub>H</sub> |

| TF1                    | Timer 1 interrupt     | 001B <sub>H</sub> |

| RI + TI                | Serial port interrupt | 0023 <sub>H</sub> |

| TF2 + EXF2             | Timer 2 interrupt     | 002B <sub>H</sub> |

**Table 8. Interrupt Sources and their Corresponding Interrupt Vectors**

A low-priority interrupt can itself be interrupted by a high-priority interrupt, but not by another low priority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.

If two requests of different priority level are received simultaneously, the request of higher priority is serviced. If requests of the same priority are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence as shown in Table 9.

| Interrup             | t Source   | Priority     |

|----------------------|------------|--------------|

| External Interrupt 0 | IE0        | High         |

| Timer 0 Interrupt    | TF0        | Į.           |

| External Interrupt 1 | IE1        | $\downarrow$ |

| Timer 1 Interrupt    | TF1        | $\downarrow$ |

| Serial Channel       | RI + TI    | $\downarrow$ |

| Timer 2 Interrupt    | TF2 + EXF2 | Low          |

Table 9. Interrupt Priority-Within-Level

# **Power Saving Modes**

Two power down modes are available, the Idle Mode and Power Down Mode.

The bits PDE and IDLE of the register PCON select the Power Down mode or the Idle mode, respectively. If the Power Down mode and the Idle mode are set at the same time, the Power Down mode takes precedence. Table 10 gives a general overview of the power saving modes.

| Mode            | Entering<br>Instruction<br>Example | Leaving by                              | Remarks                                                                                                                                         |

|-----------------|------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle mode       | ORL PCON, #01H                     | - Enabled interrupt<br>- Hardware Reset | CPU is gated off CPU status registers maintain their data. Peripherals are active                                                               |

| Power-Down mode | ORL PCON, #02H                     | Hardware Reset                          | Oscillator is stopped, contents of on-<br>chip RAM and SFR's are maintained<br>(leaving Power Down Mode means<br>redefinition of SFR contents). |

**Table 10. Power Saving Modes Overview**

In the Power Down mode of operation,  $V_{CC}$  can be reduced to minimize power consumption. It must be ensured, however, that  $V_{CC}$  is not reduced before the Power Down mode is invoked, and that  $V_{CC}$  is restored to its normal operating level, before the Power Down mode is terminated. The reset signal that terminates the Power Down mode also restarts the oscillator. The reset should not be activated before  $V_{CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize (similar to power-on reset).

### **ELECTRICAL CHARACTERISTICS**

### **Absolute Maximum Ratings**

| Ambient temperature under bias (T <sub>A</sub> )                          | -40 to +85 °C           |

|---------------------------------------------------------------------------|-------------------------|

| Storage temperature (T <sub>ST</sub> )                                    | 65 to + 150 °C          |

| Voltage on V <sub>CC</sub> pins with respect to ground (V <sub>SS</sub> ) | -0.5V to 6.5V           |

| Voltage on any pin with respect to ground (VSS)                           | 0.5V to $V_{CC} + 0.5V$ |

| Input current on any pin during overload condition                        | 10mA to +10mA           |

| Absolute sum of all input currents during overload condition              | 100mA                   |

| Power dissipation                                                         | 200mW                   |

**Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for longer periods may affect device reliability. During overload conditions ( $V_{IN} > V_{CC}$  or  $V_{IN} < V_{SS}$ ) the Voltage on  $V_{CC}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

## **DC Characteristics**

### DC Characteristics for HMS99C51S/52S/54S/56S/58S

$V_{CC}\!\!=5V$  + 10%, -15%,  $V_{SS}\!\!=\!\!0V,~T_{A}\!\!=$  -40°C to 85 °C

| Daman dan                                                                                                                                                                                                                                            | 0                                      | Limit                     | Values                               | Un                               | Total Constitutions                                                                                                                                                                                                                    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------|--------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                                                                                                                                                                                                            | Symbol                                 | Min.                      | Max.                                 | it                               | Test Conditions                                                                                                                                                                                                                        |  |

| Input low voltage (except EA, RESET)                                                                                                                                                                                                                 | V <sub>IL</sub>                        | -0.5                      | 0.2V <sub>CC</sub> - 0.1             | V                                | V <sub>CC</sub> = 5.5V                                                                                                                                                                                                                 |  |

| Input low voltage (EA)                                                                                                                                                                                                                               | V <sub>IL1</sub>                       | -0.5                      | 0.2V <sub>CC</sub> - 0.1             | V                                | V <sub>CC</sub> = 5.5V                                                                                                                                                                                                                 |  |

| Input low voltage (RESET)                                                                                                                                                                                                                            | V <sub>IL2</sub>                       | -0.5                      | 0.2V <sub>CC</sub> + 0.1             | V                                | V <sub>CC</sub> = 5.5V                                                                                                                                                                                                                 |  |

| Input high voltage (except XTAL1, EA, RESET)                                                                                                                                                                                                         | V <sub>IH</sub>                        | 0.2V <sub>CC</sub> + 0.9  | V <sub>CC</sub> + 0.5                | ٧                                | V <sub>CC</sub> = 4.5V                                                                                                                                                                                                                 |  |

| Input high voltage to XTAL1                                                                                                                                                                                                                          | V <sub>IH1</sub>                       | 0.7V <sub>CC</sub>        | V <sub>CC</sub> + 0.5                | V                                | V <sub>CC</sub> = 4.5V                                                                                                                                                                                                                 |  |

| Input high voltage to $\overline{EA}$ , RESET                                                                                                                                                                                                        | V <sub>IH2</sub>                       | 0.6V <sub>CC</sub>        | V <sub>CC</sub> + 0.5                | V                                | V <sub>CC</sub> = 4.5V                                                                                                                                                                                                                 |  |

| Output low voltage (ports 1, 2, 3)                                                                                                                                                                                                                   | V <sub>OL</sub>                        | -                         | 0.45                                 | V                                | V <sub>CC</sub> = 5.5V, I <sub>OL</sub> = 1.6mA <sup>1)</sup>                                                                                                                                                                          |  |

| Output low voltage (port 0, ALE, PSEN)                                                                                                                                                                                                               | V <sub>OL1</sub>                       | -                         | 0.45                                 | ٧                                | V <sub>CC</sub> = 5.5V, I <sub>OL</sub> = 3.2mA <sup>1)</sup>                                                                                                                                                                          |  |

| Output high voltage (ports 1, 2, 3)                                                                                                                                                                                                                  | V <sub>OH</sub>                        | 2.4<br>0.9V <sub>CC</sub> | -                                    | V                                | V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -80μA<br>V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -10μA                                                                                                                                     |  |

| Output high voltage<br>(port 0 in external bus<br>mode, ALE, PSEN)                                                                                                                                                                                   | V <sub>OH1</sub>                       | 2.4<br>0.9V <sub>CC</sub> | -                                    | ٧                                | V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -800μA <sup>2)</sup><br>V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -80μA <sup>2)</sup>                                                                                                        |  |

| Logic 0 input current (ports 1, 2, 3)                                                                                                                                                                                                                | I <sub>IL</sub>                        | -10                       | -65                                  | μА                               | V <sub>IN</sub> = 0.45V                                                                                                                                                                                                                |  |

| Logical 1-to-0 transition current (ports 1, 2, 3)                                                                                                                                                                                                    | I <sub>TL</sub>                        | -65                       | -650                                 | μА                               | V <sub>IN</sub> = 2.0V                                                                                                                                                                                                                 |  |

| Input leakage current (port 0, EA)                                                                                                                                                                                                                   | ILI                                    | -                         | ±1                                   | μА                               | 0.45 < V <sub>IN</sub> < V <sub>CC</sub>                                                                                                                                                                                               |  |

| Pin capacitance                                                                                                                                                                                                                                      | C <sub>IO</sub>                        | -                         | 10                                   | pF                               | f <sub>C</sub> = 1MHz<br>T <sub>A</sub> = 25°C                                                                                                                                                                                         |  |

| Power supply current: Active mode, 4MHz <sup>3)</sup> Idle mode, 4MHz <sup>4)</sup> Active mode, 24 MHz <sup>4)</sup> Idle mode, 24MHz <sup>4)</sup> Active mode, 40 MHz <sup>4)</sup> Idle mode, 40 MHz <sup>4)</sup> Power Down Mode <sup>4)</sup> | Icc<br>Icc<br>Icc<br>Icc<br>Icc<br>Icc | -                         | 8<br>4<br>25<br>10<br>30<br>15<br>50 | mA<br>mA<br>mA<br>mA<br>mA<br>mA | V <sub>CC</sub> = 5V <sup>4</sup> )<br>V <sub>CC</sub> = 5V <sup>5</sup> )<br>V <sub>CC</sub> = 5V <sup>4</sup> )<br>V <sub>CC</sub> = 5V <sup>5</sup> )<br>V <sub>CC</sub> = 5V <sup>4</sup> )<br>V <sub>CC</sub> = 5V <sup>6</sup> ) |  |

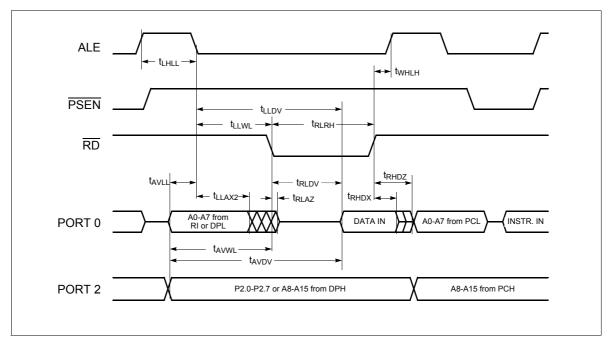

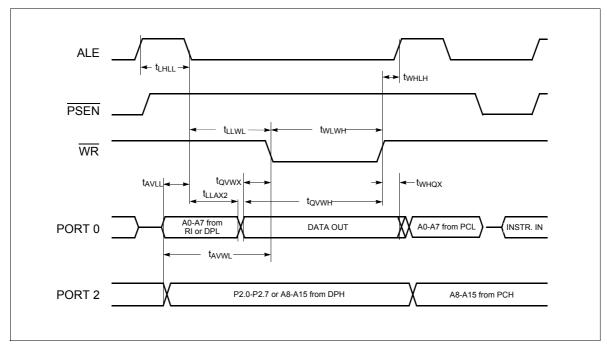

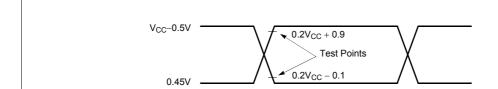

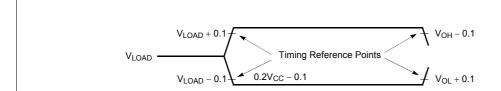

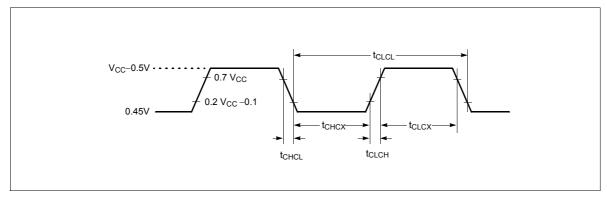

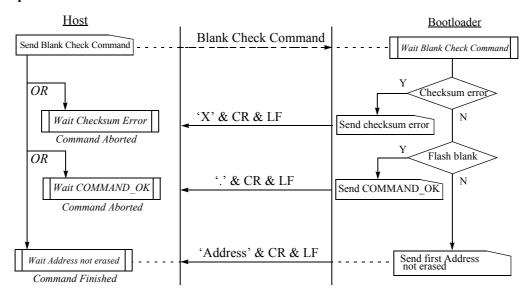

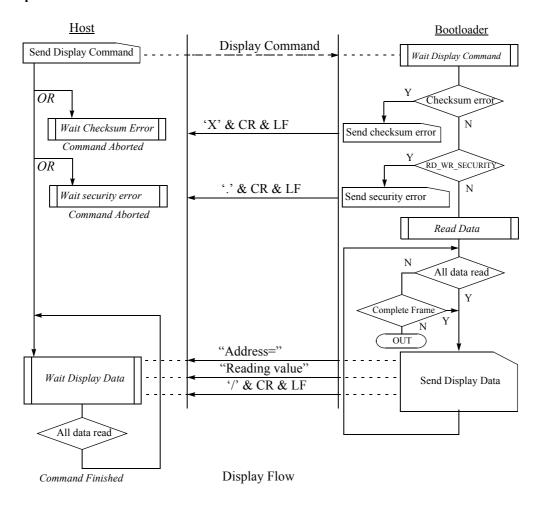

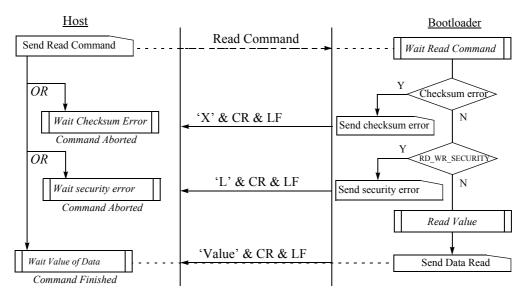

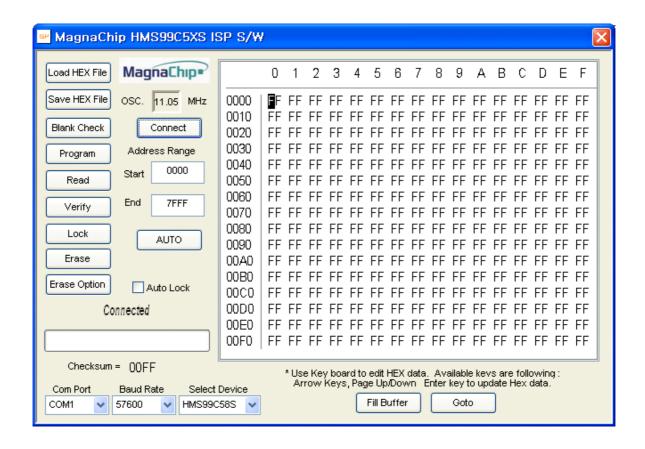

- 1) Capacitive loading on ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub> of ALE and port 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operation. In the worst case(capacitive loading: > 50pF at 3.3V, > 100pF at 5V), the noise pulse on ALE line may exceed 0.8V. In such cases it may be desirable to qualify ALE with a schmitt-trigger, or use an address latch with a schmitt-trigger strobe input.